Introduction

High Speed PCB power integrity is a critical challenge in modern electronics, particularly for systems operating at gigabit data rates and sub-nanosecond switching speeds. As digital circuits push toward higher frequencies, stable power delivery becomes increasingly difficult, mainly due to simultaneous switching noise (SSN), ground bounce, and electromagnetic interference (EMI).

These power integrity issues do not exist in isolation—they directly impact signal integrity, leading to timing violations and degraded system performance. Unlike low-speed designs, where simple bulk capacitors can suffice, high-speed PCBs demand carefully engineered power distribution networks (PDNs) to manage transient current demands and maintain voltage stability across a broad frequency spectrum.

The underlying difficulty arises from the frequency-dependent behavior of power delivery systems. At high frequencies, parasitic inductances, capacitive coupling, and transmission line effects dominate, making precise PDN design essential for reliable system operation.

Power Integrity Definition and Core Challenges

Power Integrity encompasses the comprehensive management of voltage stability, noise suppression, and current distribution across all frequency domains within electronic systems. In high-speed applications, this extends far beyond simple DC voltage regulation to include AC impedance control, transient response optimization, and electromagnetic compatibility considerations.

Critical High Speed PCB Power Challenges

Simultaneous Switching Noise (SSN) emerges when multiple high-speed I/Os transition simultaneously, creating significant current transients that excite resonant modes within the power distribution network. These transients can generate voltage fluctuations exceeding several hundred millivolts, sufficient to cause logic state uncertainties and timing violations.

Ground bounce manifests as common-mode voltage variations between local and reference ground potentials, particularly problematic in high pin-count components where return current paths experience impedance discontinuities. This phenomenon directly impacts signal integrity through reference level shifts and increased electromagnetic emissions.

IR drop analysis becomes critical when dealing with power-hungry processors drawing tens of amperes through PCB traces and vias. Voltage drops across copper conductors can create local supply variations that impact component performance margins and thermal management.

PDN impedance resonance occurs when inductive and capacitive elements within the power delivery path create underdamped oscillations at specific frequencies, potentially amplifying noise rather than suppressing it.

Factors Influencing Power Integrity Performance

PCB Stackup Architecture and Power Plane Design

Effective high-speed PCB stackup design requires careful consideration of power and ground plane spacing to maximize inter-plane capacitance while minimizing parasitic inductance. Optimal designs typically employ plane separations between 2-6 mils, creating distributed capacitance values ranging from 50-200 pF per square inch.

Power plane segmentation strategies must balance current capacity with noise isolation requirements. Solid planes provide the lowest impedance paths but may require strategic splits to prevent noise coupling between sensitive analog and high-speed digital sections.

Decoupling Capacitor Network Optimization

PCB decoupling capacitors form the backbone of any effective power integrity strategy, yet their implementation requires precise understanding of parasitic effects and frequency domain behavior. The equivalent series inductance (ESL) of standard surface-mount capacitors limits their effectiveness above their self-resonant frequency, typically creating impedance valleys followed by inductive regions.

Effective decoupling strategies employ parallel combinations of different capacitor values to extend the useful frequency range. A typical high-speed digital design might use 470µF bulk capacitors for low-frequency transients, 10µF ceramics for mid-frequency response, and 0.1µF components for high-frequency decoupling.

Capacitor placement optimization demands minimal loop areas between power pins, decoupling capacitors, and ground connections. Via inductance becomes a critical factor, with each via contributing approximately 0.3-0.5 nH of parasitic inductance that directly impacts high-frequency performance.

PDN Impedance Modeling and Analysis

Power distribution network impedance characterization requires consideration of all contributing elements including power planes, via transitions, package parasitics, and discrete decoupling components. Target impedance levels typically fall below 100 mΩ for high-performance digital applications, requiring sophisticated modeling to achieve across the entire operational frequency spectrum.

Advanced Power Distribution Network Design Methodology

Frequency Domain PDN Characterization

Modern High Speed PCB power integrity analysis demands comprehensive frequency domain modeling to understand impedance behavior from DC through several gigahertz. The PDN impedance spectrum exhibits distinct regions dominated by different physical phenomena.

Below 100 kHz, bulk capacitors and voltage regulator output impedance control system behavior. From 100 kHz to 10 MHz, intermediate value ceramics provide the primary impedance control. Above 10 MHz, small value ceramics, power plane capacitance, and package parasitics become dominant factors.

Impedance target methodology requires establishing maximum allowable PDN impedance based on acceptable voltage ripple levels and transient current demands. For typical high-speed digital applications, target impedances range from 10-100 mΩ depending on current levels and noise tolerance requirements.

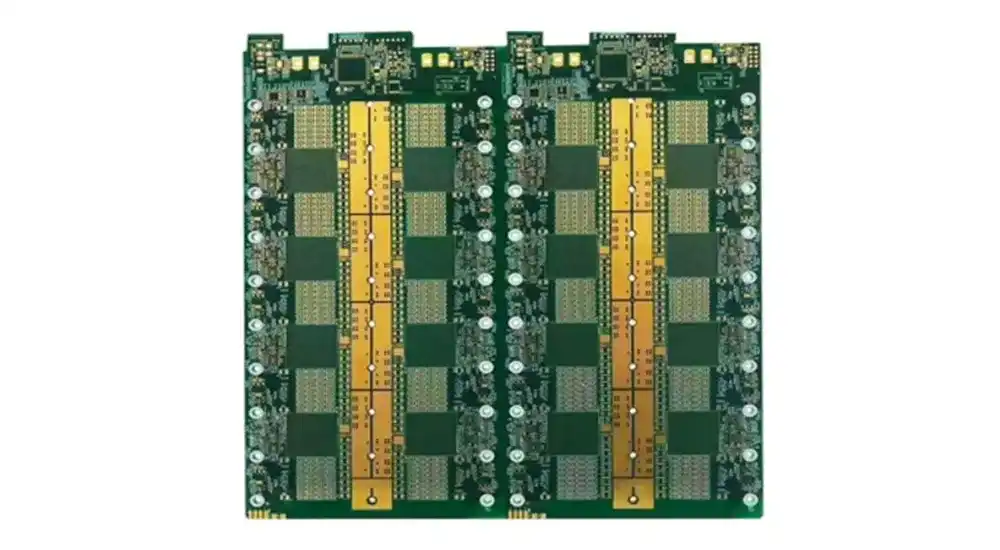

Multi-Layer Power Plane Architecture

Sophisticated controlled impedance in high-speed PCB layout extends to power delivery systems through careful plane geometry design. Power plane thickness, copper weight, and dielectric properties all influence current carrying capacity and impedance characteristics.

Via stitching strategies provide critical connections between plane layers while minimizing impedance discontinuities. Optimal via patterns employ regular grids with spacing typically less than λ/10 at the maximum frequency of interest, ensuring effective electromagnetic coupling between planes.

Power island design enables voltage domain isolation while maintaining low impedance within each domain. This technique proves particularly valuable in mixed-signal applications where analog and digital sections require separate supply management.

Material Selection for Power Integrity

High-speed PCB materials significantly impact power delivery performance through their dielectric properties and loss characteristics. Low-loss materials reduce power plane attenuation but may increase resonant peak amplitudes, while higher-loss materials provide natural damping at the cost of increased power dissipation.

Embedded capacitance materials offer unique advantages for power integrity applications by providing distributed capacitance with minimal parasitic inductance. These specialized dielectrics can achieve capacitance densities exceeding 1000 pF per square inch while maintaining controlled impedance characteristics.

High Speed PCB Manufacturing

Power and Signal Integrity Interaction

Signal integrity and power integrity exhibit complex interdependencies in high-speed systems. Power supply noise directly modulates signal edge rates, creating timing jitter and reducing noise margins. Conversely, signal switching transients generate power supply disturbances through return current fluctuations and capacitive coupling mechanisms.

Return path design becomes critical when considering crosstalk and EMI in high-speed PCB applications. Discontinuous return paths force current through alternate routes, creating voltage drops and electromagnetic emissions that impact both power and signal integrity.

EMI/EMC considerations require coordinated power and signal integrity design approaches. Effective power delivery systems naturally reduce electromagnetic emissions by providing low-impedance current paths and minimizing voltage fluctuations that can drive antenna structures within the PCB.

Practical Implementation Strategies

Design Phase Power Integrity Planning

Successful power integrity implementation begins during initial architecture definition rather than post-layout optimization. Early decisions regarding component selection, power domain partitioning, and stackup architecture establish fundamental constraints that cannot be easily modified later in the design cycle.

Simulation-driven design methodology enables predictive analysis before committing to physical implementation. AC impedance analysis reveals resonant frequencies and impedance peaks that guide capacitor selection and placement strategies.

Manufacturing and Assembly Considerations

Power integrity vs signal integrity requirements may create conflicting manufacturing constraints that require careful balance. High-speed PCB surface finishes affect both signal propagation and power delivery characteristics, with selections requiring consideration of both domains.

Component assembly processes impact power integrity through parasitic variations and thermal cycling effects. Solder joint reliability becomes particularly critical for decoupling capacitors where connection resistance directly impacts high-frequency performance.

Verification and Testing Approaches

High-speed PCB testing methods for power integrity validation require specialized equipment and measurement techniques. Time domain reflectometry (TDR) measurements can characterize PDN impedance behavior, while power supply noise measurements during functional operation verify design effectiveness.

Real-world validation often reveals power integrity issues not predicted by simulation, particularly related to thermal effects, manufacturing variations, and component aging. Comprehensive test strategies should include worst-case loading conditions and temperature variations.

Engineering Recommendations and Best Practices

Systematic Approach to PDN Optimization

Effective how to improve power integrity in high speed PCB implementations require systematic approaches addressing multiple frequency decades simultaneously. Begin with target impedance definition based on application requirements, then work backwards to determine required capacitance and placement strategies.

Common power integrity issues in high speed PCBs typically stem from insufficient high-frequency decoupling, inadequate return path planning, or resonant frequency alignment with signal content. Prevention requires early identification of potential problem areas and proactive design measures.

Advanced Design Techniques

Decoupling capacitor placement for power integrity optimization extends beyond simple proximity rules to consider current loop minimization and parasitic inductance control. Multiple small capacitors often outperform single large ones due to reduced loop inductance and improved current sharing.

Power distribution network design for high frequency PCB applications benefits from distributed approaches that treat power delivery as a transmission line system rather than simple DC distribution. This perspective guides via design, plane geometry, and interconnection strategies.

Conclusion

Power integrity is a critical aspect of high-speed PCB design, requiring a thorough understanding of frequency-dependent behavior, parasitic effects, and system-level interactions. Achieving robust power integrity demands careful integration of material selection, stackup architecture, component placement, and verification methodologies throughout the entire design and production process.

As modern high-speed systems become increasingly complex, power integrity serves as a key differentiator for product performance and reliability. Designers must address power delivery as a fundamental system requirement rather than an afterthought to signal routing.

At Haoyue Electronics, we combine advanced design expertise with precise manufacturing capabilities to ensure reliable power integrity in high-speed PCB applications. Our services include:

- Comprehensive power integrity solutions – from PDN design and decoupling optimization to verification and testing

- Stackup and material expertise – ensuring low-impedance power delivery and minimal parasitic effects

- System-level verification – simulation and measurement to validate power integrity under dynamic conditions

- Prototype-to-production support – consistent power integrity practices across all manufacturing stages

Effective power integrity design ultimately supports signal integrity and overall system performance, forming a foundation for high-speed electronic systems across diverse applications. Contact us today to discuss your project requirements and explore how Haoyue Electronics can help deliver high-performance, reliable PCB solutions tailored to your application needs.